Chester Rebeiro Debdeep Mukhopadhyay Sarani Bhattacharya

# Timing Channels in Cryptography A Micro-Architectural Perspective

Timing Channels in Cryptography

Chester Rebeiro • Debdeep Mukhopadhyay Sarani Bhattacharya

## Timing Channels in Cryptography

A Micro-Architectural Perspective

Chester Rebeiro Columbia University New York New York USA

Debdeep Mukhopadhyay Indian Institute of Technology Kharagpur West Bengal India Sarani Bhattacharya Department of Computer Science and Engin IIT Kharagpur Kharagpur India

ISBN 978-3-319-12369-1 ISBN 978-3-319-12370-7 (eBook) DOI 10.1007/978-3-319-12370-7

Library of Congress Control Number: 2014954350

Springer Cham Heidelberg New York Dordrecht London

© Springer International Publishing Switzerland 2015

This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

The publisher, the authors and the editors are safe to assume that the advice and information in this book are believed to be true and accurate at the date of publication. Neither the publisher nor the authors or the editors give a warranty, express or implied, with respect to the material contained herein or for any errors or omissions that may have been made.

Printed on acid-free paper

Springer is part of Springer Science+Business Media (www.springer.com)

#### Foreword

With the publication of the Data Encryption Standard DES in 1977 and the invention of public key cryptography in the 1980s, cryptography has moved into civil applications. This was pushed by the electronic revolution, which needs cryptography to create an electronic equivalent of the real world into the digital world. Cryptography is used to provide confidentiality, digital signatures, anonymity, payments, electronic transactions, elections, and many more.

Cryptography and cryptographic protocols by themselves do not provide security: they need a digital platform that executes the algorithms and protocols. In the early days, these platforms were computers and servers sitting in well protected computer rooms and offices. The main concern when implementing the algorithms and protocols was efficiency, as cryptographic algorithms are typically very computationally demanding. The attacker model assumed that the computer platforms themselves were well protected and that only the result of the encryption, the ciphertext, has to travel over insecure communication channels, such as cables or satellite communication or tapes that are transported between bank offices and the bank headquarters.

However, as the electronic revolution expanded, electronics became cheaper, more widespread, and integrated into day to day applications. Examples are pay TV systems, banking cards, identity cards, or access control systems. This omnipresence of electronic gadgets changes the attacker model! Now, the implementation becomes the weak link in the chain: the attacker will attack *while* the electronic device is performing cryptographic operations using the secret key operating on possible sensitive data. During calculations, the devices leak information. These are the so-called side channel attacks. The attacker will observe the device while it performs its calculations. From timing or power consumption variations, or from electromagnetic radiations, the attacker is able to guess which operations and which sensitive data is being handled.

The contributions of this book are situated in this context. One highly important source of side channel information leakage is the timing variations of calculations. Cryptographic algorithms and protocols are written in high level languages and compiled onto sophisticated digital platforms. Both the software stack and the hardware platform include a large variety of optimizations to improve performance. Memory accesses and branches are expensive in execution time, therefore processors include caches and branch predictors. Unfortunately, these optimizations result in timing variations when executing a program. Caches are considered one of the most important sources of side channel information leakage. This book therefore gives a comprehensive overview and an in depth analysis of many flavors of attacks using caches and branch predictors. It ends with a set of countermeasures to address these timing attacks at different abstraction layers.

This book is a fine read for anyone interested in the many possibilities of cache attacks. A software engineer should not write any line of a cryptographic routine without knowing how powerful timing attacks are. This book gives a clear insight on how these attacks work and how they can be mitigated. Enjoy reading!

Leuven, Belgium December 2014 Ingrid Verbauwhede

#### Preface

Cryptography plays a vital role in securing e-business and e-commerce transactions. The algorithms used have been rigorously analyzed and tested for their ability to conceal information. However, these algorithms are needed to be realized in systems that are used in a variety of applications. As the saying says, *there's many a slip 'twixt the cup and the lip*, these implementations may leak sensitive information via unintended timing channels. Over the past 20 years, several attacks have been developed that use these *side-channels* to reveal secrets from ciphers. These attacks, known as timing attacks, are powerful enough to break a mathematically robust cipher in few minutes on standard computing platforms.

Starting from its inception to the present day, timing attacks and the underneath statistics have evolved. Enhancements made to computer architecture over the years have also influenced timing channels. To develop a system secure against these threatening channels, one needs to be abreast of the interplay between cryptographic algorithms and computer architecture. Here is where this book steps in. It brings on a single platform aspects of computer architecture and cryptography that are essential to understand *how* timing attacks work and *why* they work. It describes the attacks and analyzes the relationship between the cipher implementation, system micro-architecture, and the attack threat. Various timing channels arising due to cache memories and branch prediction units are presented. The book would help engineers and researchers understand timing attacks and thereafter develop platforms that can tolerate these attacks.

The following topics are covered.

• **Modern Cryptography.** Attackers make use of the cipher's structure to extract the secret key from execution time. The attacks are made even more powerful when ideas from classical cryptanalysis are used with the timing information. The book therefore begins with a review of a variety of modern ciphers ranging from symmetric algorithms like the Advanced Encryption Standard (AES) to asymmetric algorithms like the Rivest-Shamir-Adleman (RSA), and some popular classical cryptanalysis techniques.

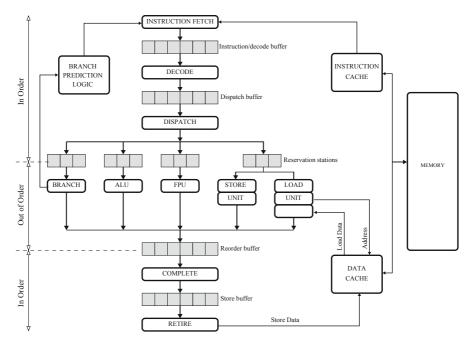

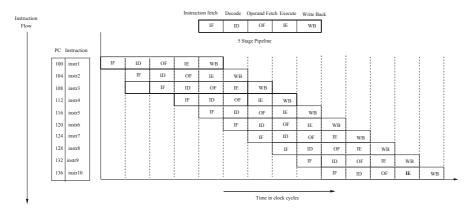

- **Superscalar Processor Architectures.** To address how timing channels arise in a system, the book provides a background of the internal micro-architecture of processors. An introduction to modern superscalar architectures has been provided, with an emphasis on the components in them that affect the execution time of ciphers.

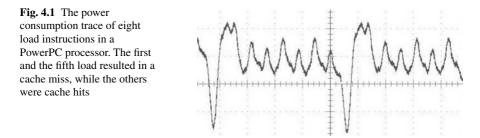

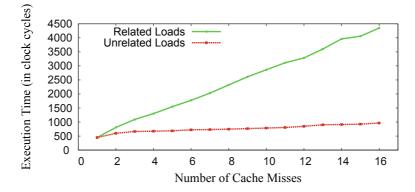

- **Time-Driven Cache Attacks on Block Ciphers.** Memory load instructions that cause a cache miss takes considerably longer than those that result in a cache hit. Attackers utilize this difference to build a variety of attacks on block ciphers. A detailed discussion on how these attacks are implemented is presented, with emphasis on various accurate time measurement techniques and analysis methods to observe the cache hit miss phenomenon.

- Advanced Time-Driven Cache Attacks on Block Ciphers. Combination of classical cryptanalysis with side-channel attacks paves way to powerful attack methodologies. A combination of classical differential cryptanalysis with cache timing attacks has been discussed in the book to describe this threat.

- Formal Analysis of Time-Driven Cache Attacks. Developing suitable metrics for comparison of secured implementations and using them to guide the design flow is an important aspect in security engineering. In this pursuit, the book provides formal modeling of time-driven cache attacks on block ciphers and suggests metrics for evaluation and comparison of such implementations. A discourse on how micro-architectural features, such as pipelining and out-of-order execution, affect cache attacks is presented. These guidelines form a framework for developing ideal implementations of the block ciphers with respect to time-driven cache attacks.

- **Profiled Time-Driven Cache Attacks on Block Ciphers.** There are various types of cache attacks, of which profiled cache attacks are arguably the most powerful. The book provides a detailed description of such profiled attacks, which rely on building timing profiles in a learning phase before mounting the attack. The book also provides insights into developing metrics for estimating the information leakage and relates the leakage to micro-architectural features in modern computers, such as hardware prefetchers.

- Access-Driven Cache Attacks on Block Ciphers. Cache attacks come in different flavors, one of them, called access attacks, relies on a spy program running along with the encryption program. The spy uses timing measurements to determine memory access patterns made by the encryption. By monopolizing the OS scheduler, the spy program can accurately determine every memory access made, thereby leading to powerful attacks. The book provides a comprehensive overview on the topic to understand the theory and develop the procedure of such access attacks.

- Branch Prediction Attacks. Branch prediction units are artifacts in computer architectures to reduce performance penalties due to branch instructions. They predict whether a branch instruction will be taken or not taken, thereby reducing processor stalls. Athough this can boost performance of an application significantly, it can also lead to timing channels that are catastrophic. Attackers have used these channels to break mathematically strong asymmetric key ciphers such

as the RSA. Several of the attack strategies developed are discussed in detail in the book.

• **Countermeasures**. To circumvent timing attacks, a variety of countermeasures have been proposed at various levels in the system: from the application level and architectural level to the Operating System. The book tries to provide an overview on these countermeasures, how they are applied, their effectiveness, and the consequent overheads involved.

IIT Kharagpur, India November 2014 Chester Rebeiro Debdeep Mukhopadhyay Sarani Bhattacharya

#### Acknowledgements

This preface would be incomplete without a mention of the people who made this effort possible. The authors would like to express their sincere gratitude to the Computer Science and Engineering Department of IIT Kharagpur, which provides an ideal environment for research on information security. The authors would like to thank all their colleagues, students, collaborators, and funding agencies without whose support this work would not be possible. Special thanks to Abhijit Das, Partha Pratim Chakrabarty, Rajat Subhra Chakraborty, Dipanwita Roy Chowdhury, Phuong Ha Nguyen, and Indranil Sengupta from IIT Kharagpur, and Junko Takahashi (NTT Labs), Toshinori Fukunaga (NTT Labs), and Sobha PM (CDAC Bangalore) for their help and support during the project.

**Chester Rebeiro** would like to thank his family members especially his parents, wife Sharon, and son Tristan for their love and prayers.

**Debdeep Mukhopadhyay** would like to thank in particular all his family members and friends. He would like to make a special mention of his parents, wife, and brother for their bonding and wishes. He would like to dedicate this book to his daughter Debanti, who has indeed made his life more interesting.

**Sarani Bhattacharya** would like to thank her parents and friends for their continuous support and encouragement. She would also like to specially thank her mentor Prof. Debdeep Mukhopadhyay for his invaluable guidance and Dr. Chester Rebeiro for his advice and suggestions.

### Contents

| 1 | An l | Introduction to Timing Attacks                                  | 1  |

|---|------|-----------------------------------------------------------------|----|

|   | 1.1  | Side-Channel Attacks                                            | 3  |

|   |      | 1.1.1 Side-Channel Attack Requirements                          | 4  |

|   |      | 1.1.2 The Attacker's Success                                    | 5  |

|   |      | 1.1.3 Side-Channel Attack Suppression                           | 5  |

|   | 1.2  | Timing Attacks                                                  | 6  |

|   |      | 1.2.1 Kocher's Timing Attack                                    | 7  |

|   |      | 1.2.2 Taxonomy of Timing Attacks                                | 9  |

|   | 1.3  | Organization                                                    | 10 |

|   | Refe | erence                                                          | 11 |

|   |      |                                                                 |    |

| 2 |      | lern Cryptography                                               | 13 |

|   | 2.1  | Types of Encryption Algorithms                                  | 13 |

|   | 2.2  | Block Ciphers: An Important Family of Symmetric-Key Ciphers     | 15 |

|   |      | 2.2.1 AES                                                       | 16 |

|   |      | 2.2.2 CLEFIA                                                    | 20 |

|   |      | 2.2.3 CAMELLIA                                                  | 23 |

|   | 2.3  | Classical Cryptanalysis                                         | 24 |

|   |      | 2.3.1 Classical Cryptanalysis of Block Ciphers                  | 25 |

|   |      | 2.3.2 The Idea of Differential in Block Ciphers                 | 25 |

|   | 2.4  | Asymmetric-Key Ciphers                                          | 29 |

|   | 2.5  | RSA: An Asymmetric-Key Algorithm                                | 29 |

|   |      | 2.5.1 Square and Multiply Algorithm to Perform Exponentiation . | 30 |

|   | 2.6  | Confinement Problem and Covert Channels                         | 31 |

|   | 2.7  | Formal Analysis of Side-Channel Attacks                         | 32 |

|   | 2.8  | Conclusion                                                      | 33 |

|   | Refe | erences                                                         | 34 |

| 3 | Sup  | erscalar Processors, Cache Memories, and Branch Predictors      | 37 |

|   | 3.1  | Superscalar Processors                                          | 37 |

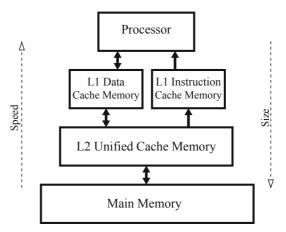

|   | 3.2  | Memory Hierarchy and Cache Memory                               | 39 |

|   |      | 3.2.1 Organization of Cache Memory                            | 40 |

|---|------|---------------------------------------------------------------|----|

|   |      | 3.2.2 Improving Cache Performance for Superscalar Processors  | 43 |

|   | 3.3  | Branch Prediction Unit                                        | 45 |

|   |      | 3.3.1 Static Branch Prediction                                | 47 |

|   |      | 3.3.2 Dynamic Branch Prediction Schemes                       | 47 |

|   |      | 3.3.3 Branch Target Buffers                                   | 50 |

|   | 3.4  | Conclusion                                                    | 50 |

|   | Refe | erence                                                        | 51 |

| 4 | Tim  | e-Driven Cache Attacks                                        | 53 |

|   | 4.1  | A Simple Illustration                                         | 53 |

|   |      | 4.1.1 Relation Between Size and Bits Revealed                 | 55 |

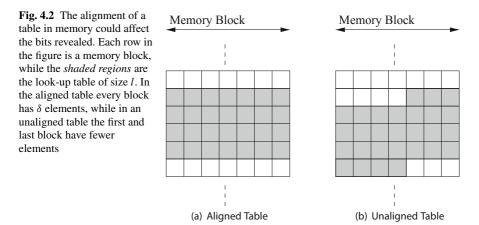

|   |      | 4.1.2 Relation Between Alignment of Tables and Bits Revealed  | 56 |

|   |      | 4.1.3 Initial State of Cache Memory                           | 56 |

|   | 4.2  | Collisions from Execution Time                                | 57 |

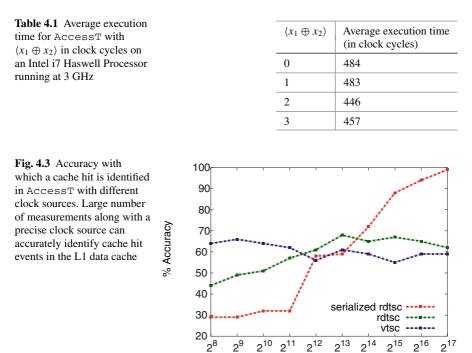

|   |      | 4.2.1 Clocks Using Hardware Time Stamp Counters               | 57 |

|   |      | 4.2.2 Clocks with Virtual Time-Stamp Counters                 | 59 |

|   |      | 4.2.3 Distinguishing Cache Hit and Miss Events Using Time     | 60 |

|   | 4.3  | Timing Attacks on Block Ciphers Based on Internal Collisions  | 63 |

|   |      | 4.3.1 Max, Min, or Max Deviation                              | 65 |

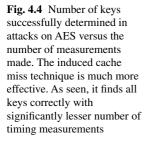

|   | 4.4  | Time-Driven Attack Based on Induced Cache Miss                | 66 |

|   | 4.5  | Results                                                       | 69 |

|   | 4.6  | Conclusion                                                    | 69 |

|   | Refe | erence                                                        | 69 |

| 5 | Adv  | anced Time-Driven Cache Attacks on Block Ciphers              | 71 |

|   | 5.1  | Second Round Attack on AES                                    | 71 |

|   | 5.2  | Differential Cache Attacks on Feistel Ciphers                 | 72 |

|   | 5.3  | Differential Cache Attack on CLEFIA                           | 75 |

|   |      | 5.3.1 Differential Properties of CLEFIA's <i>F</i> Functions  | 75 |

|   |      | 5.3.2 Determining <i>RK</i> 0 and <i>RK</i> 1                 | 76 |

|   |      | 5.3.3 Determining $WK0 \oplus RK2$ and $WK1 \oplus RK3 \dots$ | 77 |

|   |      | 5.3.4 Determining <i>RK</i> 4 and <i>RK</i> 5                 | 78 |

|   |      | 5.3.5 Determining <i>RK</i> 2 and <i>RK</i> 3                 | 79 |

|   | 5.4  | Conclusion                                                    | 79 |

|   | Refe | erences                                                       | 80 |

| 6 | A Fo | ormal Analysis of Time-Driven Cache Attacks                   | 81 |

|   | 6.1  | Memory Access Model for a Block Cipher                        | 81 |

|   | 6.2  | Cache Misses in a Block Cipher                                | 82 |

|   | 6.3  | Average Execution Time of a Block Cipher                      | 85 |

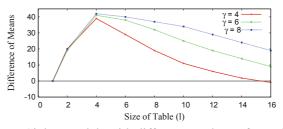

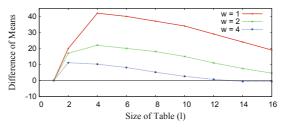

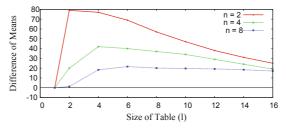

|   |      | 6.3.1 Estimating the Difference of Means                      | 87 |

|   | 6.4  | DOM as a Security Metric                                      | 88 |

|   | 6.5  | Application of the Model                                      | 90 |

|   |      | 6.5.1    | Comparing Cipher Implementations                       | 91  |

|---|------|----------|--------------------------------------------------------|-----|

|   |      | 6.5.2    | Choosing the Right Implementation                      | 92  |

|   | 6.6  | Concl    | usion                                                  | 94  |

| 7 | Prof | iled Tiı | me-Driven Cache Attacks on Block Ciphers               | 95  |

|   | 7.1  |          | tein's Cache Timing Attack                             | 95  |

|   |      | 7.1.1    | Building a Timing Profile                              | 95  |

|   |      | 7.1.2    | Extracting Keys from Timing Profiles                   | 97  |

|   | 7.2  | Cause    | s of Information Leakage                               | 98  |

|   | 7.3  |          | ifying Information Leakage in a Timing Profile         | 103 |

|   | 7.4  |          | nation Leakage due to Hardware Prefetching             | 104 |

|   | 7.5  |          | usion                                                  | 108 |

|   |      |          |                                                        | 108 |

|   |      |          |                                                        |     |

| 8 | Acce | ess-Driv | ven Cache Attacks on Block Ciphers                     | 109 |

|   | 8.1  | Acces    | s-Driven Attacks on Block Ciphers                      | 109 |

|   |      | 8.1.1    | Second Round Access-Driven Attack on AES               | 112 |

|   |      | 8.1.2    | A Last Round Access-Driven Attack on AES               | 112 |

|   | 8.2  | Async    | hronous Access-Driven Attacks                          | 113 |

|   | 8.3  | Secret   | ly Monopolizing the CPU scheduler                      | 114 |

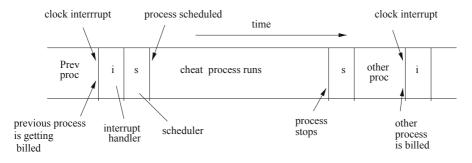

|   |      | 8.3.1    | Cheat Server                                           | 118 |

|   |      | 8.3.2    | Binary Instrumentation                                 | 119 |

|   | 8.4  | Fine C   | Grained Access-Driven Attack on AES                    | 119 |

|   | 8.5  | Attack   | Procedure                                              | 120 |

|   |      | 8.5.1    | Completely Fair Scheduler                              | 120 |

|   |      | 8.5.2    | Denial of Service Exploiting Completely Fair Scheduler | 121 |

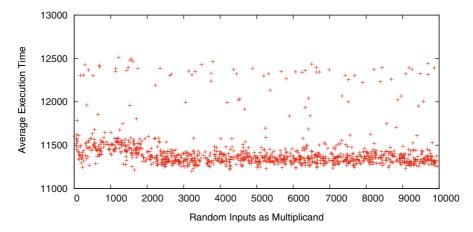

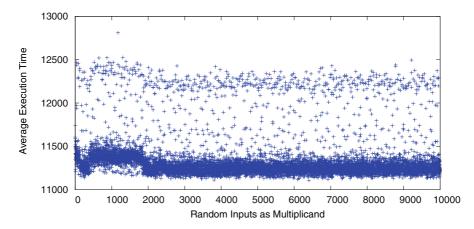

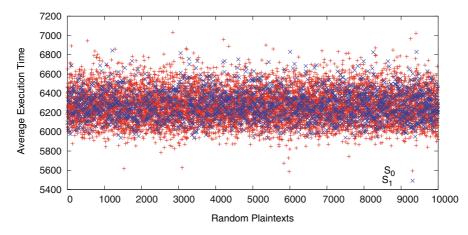

|   |      | 8.5.3    | Using Timing as Side Channel for Cache Access Attack   | 122 |

|   |      | 8.5.4    | Denoising by Neural Network                            | 123 |

|   | 8.6  | Concl    | usion                                                  | 123 |

|   | Refe | erences  |                                                        | 124 |

|   |      |          |                                                        |     |

| 9 |      |          | ediction Attacks                                       | 125 |

|   | 9.1  |          | mentation of RSA                                       | 125 |

|   |      | 9.1.1    | Square and Multiply Exponentiation Algorithm           | 125 |

|   |      | 9.1.2    | Balanced Montgomery Powering Ladder Implementation     | 126 |

|   |      | 9.1.3    | Montgomery Multiplication                              | 126 |

|   | 9.2  |          | g Branch Mispredictions                                | 127 |

|   | 9.3  |          | ting the Square and Multiply Exponentiation Algorithm  | 130 |

|   | 9.4  |          | hronous Attack on the Square and Multiply Algorithm    | 134 |

|   | 9.5  |          | ronous Attack on the Square and Multiply Algorithm     | 136 |

|   | 9.6  |          | Driven Attack Targeting the BTB                        | 136 |

|   | 9.7  |          | usion                                                  | 137 |

|   | Refe | erence.  |                                                        | 137 |

| 10 | Countermeasures for Timing Attacks              | 139 |

|----|-------------------------------------------------|-----|

|    | 10.1 Application Level Countermeasures          | 139 |

|    | 10.1.1 Countermeasures Involving Look-Up Tables | 140 |

|    | 10.1.2 Data-Oblivious Memory Access Pattern     | 142 |

|    | 10.1.3 Constant and Random Time Implementations | 142 |

|    | 10.2 Countermeasures Applied in the Hardware    | 143 |

|    | 10.2.1 Noncached Memory Accesses                | 143 |

|    | 10.2.2 Specialized Cache Designs                | 143 |

|    | 10.2.3 Specialized Instructions                 | 144 |

|    | 10.2.4 Hardware Prefetching                     | 145 |

|    | 10.2.5 Fuzzying Clocks                          | 145 |

|    | 10.3 Countermeasures in the Operating System    | 146 |

|    | 10.4 Conclusion                                 | 147 |

|    | References                                      | 147 |

|    |                                                 |     |

| Ар | pendix A: CPUs Used for Experiments             | 151 |

## List of Abbreviations

| Advanced Encryption Standard                |

|---------------------------------------------|

| Advanced Encryption Standard                |

| Binary Extend Euclidean Algorithm           |

| Branch Prediction Unit                      |

| Branch Target Buffer                        |

| Completely Fair Scheduler                   |

| Chosen Ciphertext Attack                    |

| Chosen Plaintext Attack                     |

| Central Processing Unit                     |

| Complementary Metal Oxide Semiconductor     |

| Chinese Remainder Theorem                   |

| Difference of Means                         |

| Dynamic Random Access Memory                |

| Greatest Common Divisor                     |

| Galois Field                                |

| Generalized Feistel Networks                |

| Inter Process Communication                 |

| Instruction Set Architecture                |

| Level 1                                     |

| Level 2                                     |

| Level 3                                     |

| Montgomery Multiplication                   |

| National Institute Standards and Technology |

| Network Security Services                   |

| Nippon Telegraph and Telephone Corporation  |

| Program Counter                             |

| Random Access Memory                        |

| Rivest Shamir Adleman                       |

| Side Channel Attacks                        |

| Symmetrical Multithreading                  |

| Signal to Noise Ratio                       |

| Substitution Permutation Network            |

| Static Random Access Memory                 |

| Time Stamp Counter                          |

| Virtual Time Stamp Counter                  |

|                                             |

#### Chapter 1 An Introduction to Timing Attacks

With the ever-increasing proliferation of e-business practices, great volumes of business transactions and data transmission are routinely carried out in devices ranging in scale from personal smartcards to business servers. Cryptographic algorithms are employed in order to secure these transactions and to ensure that the communicated data is only accessible by the intended parties. Exclusive access to the data (referred to as *plaintext*) is achieved by encrypting it with a *key* that is known only to the authorized parties.

Since Claude Shannon's benchmark paper on the communication theory of secrecy systems in [1], significant scientific advancements have been made in the development of cryptographic algorithms. The algorithms in use today are supported by extensive mathematical evaluations, which provide guarantees for secrecy of the plaintext and key. The guarantees for instance, ensure that an attacker would find it extremely difficult to get any information about the secret key from the ciphertext even if the plaintext and cryptographic algorithm are known. To take an example, the best known cryptanalytic attack against the popular Advanced Encryption Standard (AES) cipher would require around  $2^{126}$  operations of the cipher before any information about the key is obtained. This would take several centuries to run even with the best computing resources.

To circumvent the strict security guarantees that cryptographic algorithms comply with, attackers target the physical implementation of the algorithms rather than the algorithms itself. Irrespective of the device that the algorithm is implemented in, its execution would leave a trace in the system and the surrounding medium. The trace may reveal information about the internal state of the cipher that classical cryptanalytic attackers do not have. The mathematical proofs that guarantee security of the cipher fail when such additional information is known. This results in attacks on the cipher that are considerably more practical. For instance, when the cryptographic algorithm executes on a processor, it leaves a trace in the power consumed by the device. This trace, which essentially is a modulation of the dynamic power consumption, contains information about the data being processed and has been used by attackers to retrieve the secret key of ciphers in a few hours. Such channels that leak information about the executing cipher are called *side channels*. The class of attacks that use these side channels to obtain secret information are called

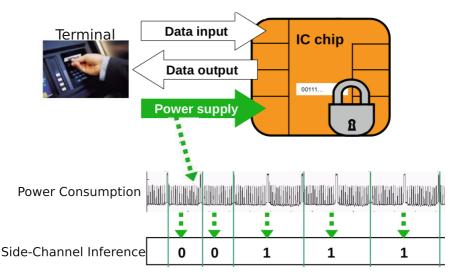

Fig. 1.1 The *power consumption* trace of a smart card reader may reveal the secret. The glitch in the trace can identify a 1 in the secret

*side-channel attacks* [2]. Figure 1.1 shows how the power consumed by a smart card reader is affected by the secret key stored in the smart card. An attacker monitoring this side can infer the smart card's secret from the glitches in the power trace.

Besides the power consumption, several other side channels have been discovered over the years. For instance, secret keys were recovered from electromagnetic radiation that emanates from a device when executing a cipher [3]. More recently, high-pitched acoustics from the vibration of electronic components have been used to recover cryptographic keys [4]. Side channels based on time have also been used to build attacks against ciphers. Information in timing channels is conveyed by the variation in the execution time of a piece of code [6]. As an example, consider the function Divide in Listing 1.1. The function generally returns the quotient when *a* is divided by *b*. However, if *b* happens to be 0, then the function returns an error value.

**Listing 1.1** Function divide returns the quotient of a/b

```

unsigned int Divide (unsigned int a, unsigned int b) {

if (b== 0)

return ERROR;

else

return a/b;

}

```

Since no division is performed when b = 0, the function finishes a bit earlier compared to when  $b \neq 0$ . An observer who can only monitor the execution time of Divide, would therefore be able to identify invocations when b = 0. Further information about b may be obtained from the execution time if the hardware used for division depends on the divisor length. A division where the divisor is large would complete earlier than a division with a small divisor.

Variation in the execution time of Divide is due to the effect of the input *b* on the conditional statements and underlying hardware. Conditional statements alter the execution path of the function. This may affect execution time if, for instance, one path is substantially more longer than another. Hardware components in the system could also affect execution time. For example, data present in the cache memory would take considerably less time to load compared to when the data is accessed from the RAM. Other components in the system such as branch prediction units, memory interface units, and ALU blocks may also affect execution time of the program. Microarchitectural features in the processor such as symmetrical multithreading, prefetching, parallelization, pipelining, input–output ports, also influence execution time, albeit in a subtle manner.

To a neophyte it may seem trivial to overcome side-channel attacks by adding noise, randomizing, or fuzzing the side channels of the system. While these additions may successfully stymic certain side-channel attacks, there are still considerable number of attacks that are capable of dealing with such naïve countermeasures. In many of these cases, surprisingly, little extra effort is required to overcome the countermeasures. This book takes a look at how various features in the architecture and program structure are exploited to build time-based side-channel attacks against cryptographic ciphers. It determines how the program design and the choice of architectural components in the system can affect the success of the attacks. In this chapter we provide a brief introduction to side-channel attacks, before introducing timing side channels and the various categories of timing attacks.

#### 1.1 Side-Channel Attacks

The idea of using side channels to steal information has been used for over a century. In World War I, the telephones used in battle fields had just one wire and used the earth to carry the return current. Spies would insert rods in the ground and connect them to amplifiers in order to pick up enemy conversation. During World War II, Bell Labs were the first to discover that electromagnetic emissions from devices could be used for spying. They were able to reveal 75 % of the plaintext that was sent in a secured fashion from a distance of over 80 ft. During the 1950s, the Americans used radiations from encoding machines to spy on encrypted Russian message transmission. By building an appropriate device, it was possible to rebuild messages without decryption. These attacks were studied by American scientists under the code name Tempest, in order to identify shields for equipment. It was initially thought that side-channel attacks would require sophisticated tools that were available only to governments. In 1985, Win van Eck published the first unclassified report which showed how low cost equipment could be used to eavesdrop on messages from a distance of a few hundred meters using the emanations from cathode ray tube monitors. The equipment required an antenna tuned to receive radio transmissions

from the monitor, and could efficiently reconstruct the images that were displayed on the monitor.

More recent studies show how emissions from cables of LCD monitors, wireless keyboards, and LED indicators can be picked up and decoded from several feet away. In the mid-1990s two seminal papers by Paul Kocher showed how execution time and power consumption could be used to easily retrieve secret keys from naïve implementations of cryptographic ciphers. Subsequently, substantial research activities have been directed to understanding side-channel attacks and implementing defenses. The challenge of side-channel attacks comes from the fact that it violates classical notions of cryptography. Side channels expose the fragility of a mathematically sound cipher, making it unsuitable for security applications. Hence a deeper, thorough, and theoretical study of the topic is required. In this section, we provide an overview of the side-channel attacks on cryptographic ciphers.

#### 1.1.1 Side-Channel Attack Requirements

There are three essential requirements in order that a side-channel attack be successfully carried out. These are a perturbation, manifestation, and an observation. We discuss each of these requirements below.

- 1. **Perturbation :** A perturbation occurs when the secret that the attacker wants to reveal alters the behavior of the system or its state. For instance, in Listing 1.1, the divisor *b* alters the program execution. Depending on the value of *b*, the result of conditional statements are altered, thus affecting the instructions that are executed. The behavior of the hardware divider may vary depending on the divisor *b*. Additionally, hardware registers that hold intermediate results in the divider may be perturbed during the computations. These perturbations in the behavior or system state contain information about the secret divisor *b*.

- 2. **Manifestation :** Most often the perturbations in the system, brought about by the execution, cannot be directly accessible by an attacker. In many cases however, they are manifested through side channels, which are generally more accessible. For instance, changes in register values are not always visible to a user executing an application; however, the changes are manifested in the power consumption and electromagnetic radiation of the device. The instructions executed by the program are manifested in the execution time as well as the radiation and power consumption. These manifestations provide information about the program's internals.

- 3. Observation : An attacker would have to observe the side channels in order to obtain the required information about the secret. For example, the power consumption channel would require the attacker to obtain a physical device and monitor its dynamic power consumption through an oscilloscope. For radiation measurements, the attacker would need a receiver and be close enough to pick up emissions from the device. Time-based side channels would require monitoring

#### 1.1 Side-Channel Attacks

of execution time. The clock used to measure time would need to be highly precise in order to distinguish between microarchitectural events in the execution. In certain cases the attacker could create an environment which forces the program or system to behave in a specified way.

#### 1.1.2 The Attacker's Success

Even if the three requirements for a side-channel attack are fulfilled, the attacker may not always be successful in discovering the secret. The amount of success the attacker achieves would depend on additional factors. First, the success would depend on how effectively perturbations convey the secret. For instance, in the function Divide in Listing 1.1, the perturbations due to the conditional statement result in only one value of the divisor to be detected (i.e. when b = 0). An attacker would be able to identify cases only when the divisor (b) is zero. All other divisors cannot be distinguished. On the other hand, perturbations in the execution time due to a nonconstant time hardware divider would be able to convey more information about the divisor.

The manifestation of the perturbations through side channels also affects the success of the attack. Perturbations which are well manifested would be more easy to detect. Considering the Divide function again, the presence or absence of the divide operation due to b = 0 or  $b \neq 0$  has a higher impact on the execution time of the function compared to the subtle variations in time inflicted by the divisor on the divide hardware. As a result, it is easier for an attacker to detect a division compared to detecting the differential behavior of the divider.

A third factor affecting the attack's success is the noise in side channel. Most sidechannels are extremely noisy. Further, the amount of noise and their characteristics vary between systems, processors, technologies used, and even depends on the time when measurements are made. An attacker could eliminate a significant amount of noise by signal processing, filtering, and applying other heuristics. Noise, which are uniformly distributed can be eliminated by averaging, provided the attacker is capable of making sufficient number of measurements.

#### 1.1.3 Side-Channel Attack Suppression

Side-channel attacks can be prevented by suppressing or preventing at least one of the afore mentioned requirements. While it is difficult to completely eliminate the perturbations in the system caused when a program executes, the information they convey can be hidden—for instance by masking the secret. Systems could be designed so that manifestations of the perturbations can be eliminated. Take for example, Listing 1.1. The Divide function can be rewritten so that a division is always carried out irrespective of the value of b, for instance, by performing a dummy division when b = 0. Further, the division hardware could be redesigned to ensure that the time taken is independent of the value of the divisor b, thereby preventing

any timing channels that occur in the divide operation. Registers in the system can be manufactured in such a way that the power consumed does not depend on the data it stores. As a final resort, the systems could be shielded to ensure that side-channel observations are not made. Electromagnetic shields for instance could be used to prevent radiation-based side-channel attacks. Precision clocks in the system could be disabled to ensure high resolution timers are not available to an attacker, thereby mitigating timing side channels.

Such suppression techniques do not completely protect and in many cases come with large overheads. Consider for instance, huge noise generation circuits added to a mobile phone in order to hide side-channel leakage. This would not only make the phone more bulky but also increase its cost. Worse still would be a large electromagnetic shield around the phone to prevent leakage through radiation. Building efficient and low overhead countermeasures for side-channel attacks is still an open research problem.

#### **1.2 Timing Attacks**

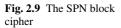

Time has always been known to contain information but it was not until 1977 that Schaefer, Gold, Linde, and Scheid published a research paper showing how time could be used to carry information [6]. They showed how a timing channel could be established between two programs in a system to communicate covertly. Information can be transferred from one program to another by the amount of time a sender holds the CPU. For instance, holding the CPU for 10, 20, or 30  $\mu$ s, can be used to represent a 0, 1, or 2 respectively. Over the years several covert timing channels have been discovered. The rate at which a program performs paging, schedules disks, utilizes cache memory, and scheduled to execute in a CPU have been used to transfer information between two collaborating programs.

In 1996, Kocher published the first timing attack against a cryptographic cipher. He used the variance in the execution time of a cipher to predict secret information. This attack kindled interest in the cryptography community and spurred research in the area, resulting in several papers published on timing attacks and defenses on a variety of ciphers. Timing attacks use the fact that the time required to perform an operation varies depending on the cipher's inputs. The inputs, comprising of a plaintext and key, undergo a series of mathematical operations before the encrypted message is obtained. The mathematical operations performed during encryption affects results of conditional statements, branch destinations, the number and type of instructions executed, instruction operands, and the memory locations accessed by the program. These are the perturbations in the system and could potentially contain information about the secret plaintext and key.

There are two ways by which a timing attacker could monitor these perturbations. The first is by timing executions of the cipher. This works since many of the perturbations in the system made during the execution of the cipher directly affects the execution time. For instance, the pattern with which cache hits and misses occur during execution of the cipher would affect its execution time. Alternatively, measuring the perturbations made by a cipher can be done by another program (called the *spy*).

Algorithm 1.1: Modular Exponentiation

```

Input: y, x, n

Output: s = y^x \mod n

1 begin

2

s \leftarrow 1

i \leftarrow w - 1

3

4

while i \ge 0 do

s \leftarrow s^2 \mod n

5

if x[i] = 1 then

6

7

s \leftarrow s * y \mod n

8

end

9

i \leftarrow i - 1

10

end

return s

11

12 end

```

The spy would determine perturbations by monitoring the usage of various hardware components in the system during or soon after the spy executes. This indirect monitoring is generally done with timing channels. For instance, the spy could identify the memory accesses made by the cipher, by using timing to determine how cache memories are utilized.

Just like in any other side-channel attack, a timing attack has two phases: an online phase, followed by an offline phase. The *online phase* monitors the time required for certain operations to be carried out, while the *offline phase* predicts the secret key from the timing information collected. We illustrate how the two phases work by taking a look at Kocher's timing attack.

#### 1.2.1 Kocher's Timing Attack

Paul Kocher's attack was on a naïve implementation of a modular exponentiation algorithm. The algorithm takes as input three numbers y, x, and n, and determines the remainder when  $y^x$  is divided by n. This is represented as  $y^x \mod n$ . The algorithm (depicted in Algorithm 1.1) is an integral part of ciphers such as RSA (Rivest Shamir and Adleman) and DH (Diffie Hellman) based ciphers. Typically, n is public and y can be found by an eavesdropper, while the exponent x is secret. Each iteration of the loop considers a bit of x (denoted x[i] in the algorithm) starting from its most significant bit. Assuming x to be of length w bits, there are w iterations of the loop. The conditional statement in line 6 results in a multiplication being performed only if x[i] = 1. Thus, a value of x[i] = 1 results in a modular squaring followed by a modular multiplication, while a value of x[i] = 0 only has a modular squaring.

The attacker knows the value of n and wants to get x. We assume the attacker is powerful enough to be able to invoke the program (or function) which implements

Algorithm 1.1 and can choose or monitor different values of y. She can also replace x with her own exponent, which we denote  $x^*$ .

The attacker triggers the execution of the function with secret x and monitors its execution time. The execution time for the algorithm varies depending on the length of x (*i.e.*, w) and its value. This can be denoted as

$$T = e + \sum_{i=0}^{w-1} t_i , \qquad (1.1)$$

where  $t_i$  is the time required for the *i*-th iteration of the loop (i.e., corresponding to the bit x[i]) and *e* includes the measurement error, loop overhead, and all other sources of inaccuracies. For a fixed *x*, time distributions can be obtained by observing the execution time corresponding to different values of *y*. The variance of the distribution is given by

$$Var(T) = Var(e) + w \cdot Var(t).$$

(1.2)

The mathematical formalism for the encryption time and its variance is used to recover the secret *x*. The attack is iterative in the sense that the attacker discovers *x* starting from its most significant bit. She discovers bit x[b] (where  $0 \le b < w$ ) only after recovering all bits from x[w - 1] to x[b + 1].

The attacker makes a guess of  $x^*[b]$  (either 0 or 1), chooses  $x^* = (x[w-1] \parallel x[w-2] \parallel x[w-3] \parallel \cdots \parallel x[b+1] \parallel x^*[b])$ , triggers modular exponentiation, and obtains the execution time  $(T^*)$ . The difference between the time for the two executions is

$$T - T^* = [e + \sum_{i=0}^{w-1} t_i] - [t_b^* + \sum_{i=b+1}^{w-1} t_i]$$

$$= [e + \sum_{i=0}^{b-1} t_i] + t_b - t_b^*$$

(1.3)

If the guess is correct  $(x[b] = x^*[b])$ , then  $t_b = t_b^*$  and the difference between the time for the two executions is  $e + \sum_{i=0}^{b-1} t_i$ . Further, on a correct guess, the difference in the variance obtained after measuring the execution time of several exponentiation is given by

$$Var[T - T^*] = Var(e) + b \cdot Var(t).$$

(1.4)

If the guess is wrong

$$Var[T - T^*] = Var(e) + (b+2) \cdot Var(t).$$

(1.5)

In other words, a correct guess causes a reduction in variance, while a wrong guess causes the variance to increase. This distinguisher can be used to validate the guess for x[b].

#### 1.2 Timing Attacks

The accuracy with which a bit in x is determined depends on how a multiplication operation can impact the execution time of a single iteration of the loop. Modern microprocessors have hardware multipliers capable of multiplying two inputs of 32 or 64 bit in a single clock cycle. If the length of s and y are small, a single microprocessor instruction, typically taking less than a nano second would be required to perform the multiplication. In such a case, the impact of the multiplication in the execution time of an iteration is negligible. In spite of this, the multiplication could be detected with reasonable accuracy, provided sufficient amount of time measurements are collected and averaged. As the length of s and y increase beyond the range of the available hardware multiplier, multiple clock cycles would be required to perform the multiplication. Each clock cycle would typically produce a partial product. In this case, the impact of the multiplier in the execution time would increase and the multiplication will be identified with a higher accuracy.

Subsequent to Kocher's work, several timing attacks have been proposed. The attacks target a variety of ciphers, utilize different techniques, and make different assumptions about the attacker. The next part of this section attempts to classify the different timing attacks on ciphers.

#### 1.2.2 Taxonomy of Timing Attacks

**Classification Based on the Type of Cipher:** Ciphers are broadly classified as symmetric-key and asymmetric-key ciphers. The attack technique varies in each case. Timing attacks on asymmetric-key ciphers are iterative. One bit of the key is recovered at a time just as in Kocher's timing attack on the modular exponentiation algorithm. Timing attacks on symmetric key ciphers target implementations that use look-up tables. Leakage from these ciphers is due to perturbations in the cache memory present in the system.

**Classification Based on the Perturbed Component:** This classification is based on the component in the system that is perturbed by the cipher's execution. Kocher's timing attack for instance falls into a category based on the execution path, since different execution paths are taken based on the secret. The requirement for these attacks is that the conditional branch depends on the value of the cipher's secret. Further, the paths should have different execution time requirements. These attacks are generally relevant to public-key ciphers.

A closely related category of timing attacks target perturbations in the processor's branch predictor. These predictors are present in most modern processors in order to reduce the performance overheads when a branch occurs. These units automatically predict the branches during the execution of the program and fetch instructions from the new location. Branch predictors can substantially influence execution time and have been exploited by attackers to determine the secret from public key ciphers.

Perturbations made to cache memories have been used by attackers to discover secret keys from ciphers, especially block ciphers. Attacks that use cache memories require that the cipher accesses memory at locations which depend on the secret key. Timing attacks based on cache memories use the fact that a cache miss takes considerably longer time compared to a cache hit. This is manifested in the execution time.

**Classification Based on the Attacker's Capabilities:** Attackers capabilities may differ. The most powerful attacker is one who can choose the plaintext to be encrypted, trigger encryptions, accurately monitor the side channel after every instruction executed. On the other side of the spectrum, the weakest attacker is one who can only monitor execution time remotely, for instance over a network. The capabilities of the attacker would therefore dictate the attack's success.

#### 1.3 Organization

A primary goal of this book is to introduce and analyze timing attacks on block ciphers due to information leaking from cache memories in the system. The book discusses how microarchitectural features in the cache memory such as automatic hardware prefetching, nonblocking, parallel, and pipelined servicing of cache misses can influence leakage. Mathematical analysis is used to quantify this leakage. Another goal of the book is to introduce and analyze timing attacks on asymmetric key ciphers due to information leakage in the processor's branch prediction units. The instruction flow of the asymmetric ciphers can be revealed using the information leakage from the branch predictors. In this book, using timing as side channel, we discuss how the microarchitectural features can be monitored efficiently, and due to their deterministic nature they eventually result in leaking the secret instruction flow. The organization is as follows.

In Chapter 2, a brief review of modern cryptography is given. Topics addressed include an overview of encryption algorithms, their implementation, and classical cryptanalysis. Covert timing channels used for stealthy communication is introduced, and a brief introduction to formal analysis of side-channel attacks is presented.

The aim of Chapter 3 is to provide an overview of superscalar processor architecture, modern cache memories, and branch predictors used in modern computer systems. Subtle changes in these components can significantly affect information leakage from timing channels.

Chapter 4 discusses how time measurements can be accurately made on systems. Accurate time measurements are critical for the success of most timing attacks. The chapter then discusses how cache hits and misses can be distinguished from the execution time. These hits and misses are used to build a time-driven attack on a block cipher.

The information obtained from the attack presented in Chapter 4 is restricted by the size of the cache line. Chapter 5 shows how this restriction can be overcome by advanced attack strategies. The chapter shows how block cipher algorithms and their differential properties can be exploited to build powerful time-driven cache attacks.

Chapter 6 develops a framework to analyze information leakage in time-driven cache attacks. The framework is capable of analyzing modern cache memories that

are equipped with microarchitectural acceleration features such as nonblocking, parallel, pipelined, and out-of-order servicing of cache misses. The framework is used to evaluate the leakage of popular block implementations and also identify the ideal way a block cipher should be implemented.

Chapter 7 introduces profiled time-driven cache attacks. These attacks require a powerful adversary who can characterize the system behavior when the cipher is executed. The adversary's success would differ depending on the way the block cipher is implemented. Further, automatic hardware prefetching can abet the attack.

Chapter 8 provides an illustrative description of access-driven attacks on block ciphers. Just as in the attacks described in Chap. 4, these attacks track cache trace patterns made by an executing block cipher. The tracing is done by a malicious process which schedules itself in such a manner, so as to observe the cache traces of individual accesses made by the cipher. The chapter explains various strategies used by the malicious process in order to make fine-grained timing measurements to observe several microarchitectural events.

Chapter 9 starts with an introduction to the algorithms used in the implementation of the public key cipher RSA. The branch predictors play a major role in predicting results of branch conditions in the cipher. In this chapter we provide several implementations where the leakage in the conditional instructions present in RSA are exploited using time as a side channel.

In Chap. 10, we highlight some of the important countermeasures that have been proposed for time-driven attacks. These countermeasures differ in how they eliminate leakage, the location in the system that they are applied, and the performance overhead.

#### Reference

- 1. Shannon CE (1949) Communication theory of secrecy systems. Bell Syst Tech J 28, 656-715

- Kocher PC, Jaffe J, Jun B (1999) Differential power analysis, CRYPTO'99 Proceedings of the 19th Annual International Cryptology Conference on Advances in Cryptology, pp 388–397. Springer-Verlag London

- Agrawal D, Archambeault B, Rao JR, Rohatgi P (2003) The EM Side-Channel(s), Cryptographic Hardware and Embedded Systems – CHES 2002, pp 29–45, Springer, Berlin

- Genkin D, Shamir A, Tromer E (2013) RSA Key Extraction via Low-Bandwidth Acoustic Cryptanalysis, Cryptology ePring Archive, Report 2013/857

- Schaefer M, Gold B, Linde R, Scheid J (n.d.) Program Confinement in KVM/370, ACM'77 Proceedings of the 1977 annual conference, pp 404–410, ACM New York, NY, USA

- Kocher P (1996) Timing Attacks on Implementations of Diffie-Hellman, RSA, DSS, and other Systems. CRYPTO'96 Proceedings of the 16th Annual International Cryptology Conference on Advances in Cryptology, pp 104–113, Springer-Verlag, London, UK

#### Chapter 2 Modern Cryptography

The art of cryptographic algorithms is an ever evolving field. Initiating from prehistoric times, the main objective of cryptographic algorithms have been to protect and allow usage of information in a legal manner. Encryption is a process of converting a plaintext message into a piece of random-looking text, often called ciphertext. The ciphertext, ideally, should contain or transfer no information to the curious third party, often referred to as the adversary. In order to allow the intended receiver to obtain back the message from the ciphertext, every encryption algorithm is reversible. Thus, the inverse operation of obtaining back the plaintext from the ciphertext, is called decryption. According to the wisdom in cryptography, the algorithms for encryption and decryption are always published and known to even the adversary. Then what does the security rely on? The mappings (from plaintext to ciphertext and vice versa) depends on an information called the key, which is hidden from the attacker. While the goal of cryptography is to design and construct such ciphering algorithms, the objective of cryptanalysis is to develop techniques to obtain the key more efficiently than making a random guess on the key. There are different classes of cryptographic algorithms, depending on their objectives. While secrecy is the obvious requirement, there are other important goals too; for example, algorithms to guarantee the integrity of information, or methods to ensure that one cannot deny a commitment to a transaction (often called the property of nonrepudiation). Then there are algorithms which ensures that authenticity is maintained in a communication, and legal parties can trust with whom they are communicating. In this book we mainly target cryptographic algorithms, with respect to secrecy of data. But often these constructions can be used for achieving the other requirements, namely authentication and nonrepudiation. Hash functions, which are used for integrity checks are not in the scope of this book.

#### 2.1 Types of Encryption Algorithms

For ciphers, there is an encryption key  $(K_a)$  and a decryption key  $(K_b)$ , which are equal for certain classes of algorithms (called symmetric-key ciphers) and different for the other class (called asymmetric-key ciphers). The scenario of a cryptographic

<sup>©</sup> Springer International Publishing Switzerland 2015 C. Rebeiro et al., *Timing Channels in Cryptography*, DOI 10.1007/978-3-319-12370-7\_2

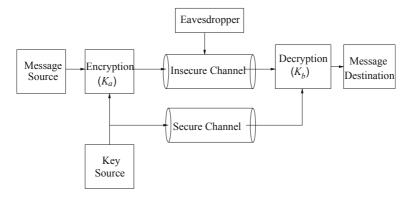

Fig. 2.1 Secret key cryptosystem model

communication is illustrated in Fig. 2.1. The encryptor uses a key  $K_a$  and the decryptor a key  $K_b$ , where depending on the equality of  $K_a$  and  $K_b$  there are two important classes of cryptographic algorithms. More precisely, the two classes of ciphers are:

- Private-key (or symmetric) ciphers: These ciphers have the same key shared between the sender and the receiver. Thus, referring to Fig. 2.1  $K_a = K_b$ .

- Public-key (or asymmetric) ciphers: In these ciphers we have  $K_a \neq K_b$ . The encryption key and the decryption keys are different.

As in symmetric-key or private-key algorithms both the encryptor and decryptor use the same key, it must somehow be securely exchanged before secret key communication can begin. The key exchange is a major bottleneck and for *n*-parties in a network, the number of key exchanges required can grow quite fast ( ${}^{n}C_{2}$  ways). However, these algorithms are often fast and are used for bulk data encryption. Two important subclasses of symmetric-key algorithms are block ciphers and stream ciphers. Block ciphers, as the name suggest operates on fixed blocks or chunks of data, while stream ciphers operate on bits or few bits of data (thus the encryption takes place like a stream!). The Advanced Encryption Standard (AES) is a very popular block cipher, while Trivium is a popular stream cipher.

Public-key algorithms, on the other hand, provide a nice solution to the keyexchange problem. In such algorithms, as we discussed the encryption and decryption keys are different. The algorithms have a key pair, consisting of (i) Public key, which can be freely distributed and is used to encrypt messages. In Fig. 2.1, this is denoted by the key  $K_a$ , and (ii) Private key, which must be kept secret and is used to decrypt messages. The decryption key is denoted by  $K_b$  in the Fig. 2.1.

In the public key or asymmetric ciphers, the two parties—often called Alice and Bob—are communicating with each other and have their own key pair. They distribute their public keys freely. Mallory (or the adversary) has the knowledge of not only the encryption function, the decryption function, and the ciphertext, but also has the capability to encrypt the messages using Bob's public key. However, she is unaware of the secret decryption key, which is the private key of the algorithm. The security of these classes of algorithms rely on the assumption that it is computationally hard or complex to obtain the private key from the public information. Doing so would imply that the adversary solves a mathematical problem which is widely believed to be difficult. It may be noted that we do not have any proofs for their hardness; however, we are unaware of any efficient techniques to solve them. The elegance of constructing these ciphers lies in the fact that the public keys and private keys still have to be related in the sense, that they perform the invertible operations to obtain the message back. This is achieved through a class of magical functions, which are called *one-way* functions. These functions are easy to compute in one direction, while computing the inverse from the output is believed to be a difficult problem. RSA is a famous public-key algorithm for this class of ciphers.

*Example 2.1* This cipher is called the famous RSA algorithm (Rivest Shamir Adleman). Let n = pq, where p and q are properly chosen and large prime numbers. Here the proper choice of p and q are to ensure that factorization of n is mathematically complex. The plaintexts and ciphertexts are  $P = C = Z_n$ , the keys are  $K_a = \{n, a\}$  and  $K_b = \{b, p, q\}$ , such that  $ab \equiv 1 \mod \phi(n)$ . The encryption and decryption functions are defined as,  $\forall x \in P$ ,  $e_{K_a}(x) = y = x^a \mod n$  and  $d_{K_b}(y) = y^b \mod n$ .

Both symmetric-key ciphers and asymmetric-key ciphers are widely studied. We provide a quick overview on some facts, which we use in the book.

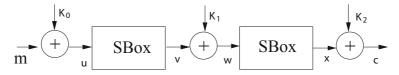

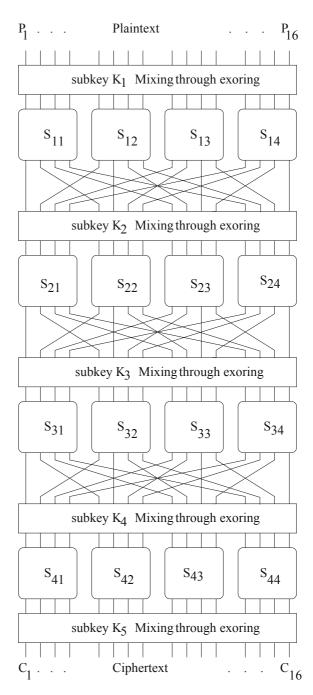

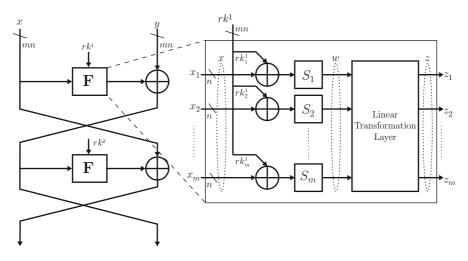

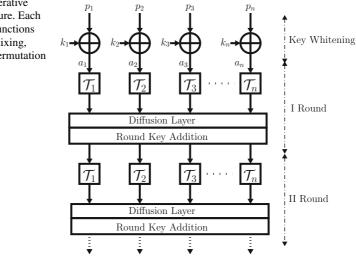

## 2.2 Block Ciphers: An Important Family of Symmetric-Key Ciphers

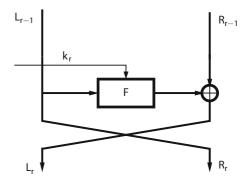

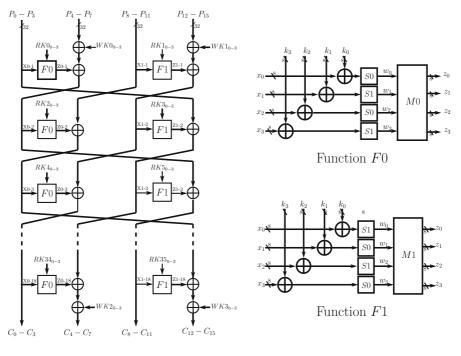

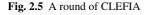

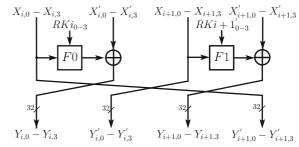

The book develops a general theory for time-driven cache attacks on block ciphers. The theory can be applied to any cipher with an iterative structure that is implemented with look-up tables. To test the theory we selected few ciphers, like AES, CAMELLIA, and CLEFIA. AES was chosen because it is the world wide standard. It has a substitution permutation network (SPN) structure and the implementation generally used has 5 large tables of 1024 bytes. The first four tables are invoked 36 times per 128-bit encryption, while the last table is invoked 16 times. Many of the latest CPUs support dedicated instructions for AES [1], on which cache attacks fail. Besides SPN, most cipher designs follow the Feistel structure (Fig. 2.2). The figure shows the rth round of a Feistel block cipher. The block is divided into two parts,  $L_r$ (Left) and  $R_r$  (Right), which are recursively computed as  $L_r = R_{r-1} \oplus \mathbf{F}(L_{r-1}, k_r)$ , and  $R_r = L_{r-1}$ . The transformation **F** is composed of several nonlinear transformations or S-Boxes, and combine the round key  $k_r$  with a portion of the block. The reversibility of the round does not depend on whether the nonlinear layer  $\mathbf{F}$  is invertible or not. The rounds are repeated for certain number of iterations to ensure sufficient security margin against known attacks.

We chose CAMELLIA as a representative of these ciphers. The third cipher we chose is CLEFIA, which has a generalized Feistel structure [2] and a round function which is conceptually similar to that of AES. Further, unlike the AES implementation considered, CLEFIA and CAMELLIA implementations used small tables of 256 bytes. This section provides a brief description of each cipher algorithm.

#### 2.2.1 AES

In 2001, the National Institute of Standards and Technology (NIST) recommended the use of Rijndael as the AES [3]. AES is a symmetric-key block cipher and can use key sizes of either 128, 192, or 256 bits to encrypt and decrypt 128-bit blocks. We summarize the AES-128 standard, which uses a key size of 128 bits. The input to AES-128 is arranged in a  $4 \times 4$  matrix of bytes called *state*. The state undergoes a series of transformations in ten rounds during the encryption process.

Algorithm 2.1 presents the AES-128 algorithm. The first operation on the input is the AddRoundKeys, which serves to provide the initial randomness by mixing the input key. The state is then subjected to nine rounds to further increase the diffusion and confusion in the cipher [4]. Each round comprises four operations on the state: SubBytes, ShiftRows, MixColumns, and AddRoundKeys. The state is then subjected to a final round, which has all operations except the MixColumns operation.

The four AES operations are defined as follows:

#### Algorithm 2.1: AES-128

```

Input: 128 bit plaintext input block x and 128 bit round keys k^{(0)}, k^{(2)}, \dots, k^{(10)} generated

from a secret key using the AES-128 key generation algorithm

Output: 128 bit ciphertext

1 begin

2

r \leftarrow 1

s^{(0)} \leftarrow \mathsf{AddRoundKeys}(x, k^{(0)})

3

while r \le 9 do

4

s^{(r)} \gets \mathsf{SubBytes}(s^{(r-1)})

5

s^{(r)} \leftarrow \mathsf{ShiftRows}(s^{(r)})

6

\mathbf{s^{(r)}} \leftarrow \mathsf{MixColumns}(\mathbf{s^{(r)}})

7

s^{(r)} \leftarrow \mathsf{AddRoundKeys}(s^{(r)}, k^{(r)})

8

9

end

s^{(10)} \gets \mathsf{SubBytes}(s^{(9)})

10

s^{(10)} \leftarrow \mathsf{ShiftRows}(s^{(10)})

11

\mathbf{y} \leftarrow \mathsf{AddRoundKeys}(\mathbf{s}^{(10)}, \mathbf{k}^{(10)})

12

return y

13

14 end

```

- AddRoundKeys : Each element in the state is subjected to a bitwise ex-or with a 128-bit round key. The round key is generated from the secret key by a key expansion algorithm as in Algorithm 2.2 [4].

- SubBytes : Each element in the state is replaced by an affine transformation of its inverse in the field  $GF(2^8)$ . For a byte  $s_i$  in the state, this operation is denoted by  $S(s_i)$ .

- ShiftRows : Provides a cyclic shift of the *i*th row in the state by *i* bytes toward the left (where 0 ≤ *i* ≤ 3). That is, each byte in the *i*th row is cyclically shifted to the left by *i* bytes.

- MixColumns : Provides a column-wise linear transformation of the state matrix. Each column of the state matrix is considered as a polynomial of degree 3 with coefficients in  $GF(2^8)$  and multiplied by the polynomial  $\{03\}\alpha^3 + \{01\}\alpha^2 + \{01\}\alpha + \{02\} \mod (\alpha^4 + 1)$ . The combination of ShiftRows and MixColumns provide the necessary diffusion for the cipher.

Key Expansion Algorithm [3] takes the secret key as input and generates round keys for 11 AddRoundKeys operations performed in AES. Key expansion as in Algorithm 2.2 uses two operations ROTWORD and SUBWORD which performs cyclic shift and substituition of four bytes  $(B_0, B_1, B_2, B_3)$  as

$$ROTWORD(B_0, B_1, B_2, B_3) = (B_1, B_2, B_3, B_0)$$

(2.1)

and

$$SUBWORD(B_0, B_1, B_2, B_3) = (SubBytes(B_0), SubBytes(B_1), SubBytes(B_2),$$

$$SubBytes(B_3)) \tag{2.2}$$

| Algorithm 2.2: Key Expansion of AES-128                              |  |  |  |  |

|----------------------------------------------------------------------|--|--|--|--|

| Input: 128 bit secret key                                            |  |  |  |  |

| <b>Output:</b> 11 round keys each of 4 words as $w[0], \dots, w[43]$ |  |  |  |  |

| 1 begin                                                              |  |  |  |  |

| $2  RCon[1] \leftarrow 01000000$                                     |  |  |  |  |

| $3 \qquad RCon[2] \leftarrow 0200000$                                |  |  |  |  |

| $4 \qquad RCon[3] \leftarrow 04000000$                               |  |  |  |  |

| 5 $RCon[4] \leftarrow 08000000$                                      |  |  |  |  |

| $6 \qquad RCon[5] \leftarrow 1000000$                                |  |  |  |  |

| 7 $RCon[6] \leftarrow 20000000$                                      |  |  |  |  |

| 8 $RCon[7] \leftarrow 40000000$                                      |  |  |  |  |

| 9 $RCon[8] \leftarrow 80000000$                                      |  |  |  |  |

| 10 $RCon[9] \leftarrow 1B000000$                                     |  |  |  |  |

| 11 $RCon[10] \leftarrow 36000000$                                    |  |  |  |  |

| 12 for $i \leq 0$ to 3 do                                            |  |  |  |  |

| 13 $w[i] \leftarrow (k[4i], k[4i+1], k[4i+2], k[4i+3])$              |  |  |  |  |

| 14 end                                                               |  |  |  |  |

| 15 for $i <= 4 to 43 do$                                             |  |  |  |  |

| 16 $temp \leftarrow w[i-1]$                                          |  |  |  |  |

| 17 <b>if</b> $i \equiv 0 \pmod{4}$ then                              |  |  |  |  |

| $18 \qquad temp = SUBWORD(ROTWORD(temp)) \oplus RCon[i/4]$           |  |  |  |  |

| 19 end                                                               |  |  |  |  |

| 20 $w[i] \leftarrow w[i-4] \oplus temp$                              |  |  |  |  |

| 21 end                                                               |  |  |  |  |

| 22 <b>return</b> $(w[0], \dots, w[43])$                              |  |  |  |  |

| 23 end                                                               |  |  |  |  |

In addition to this, AES involves a round constant term that is defined as  $RCon[1], \dots, RCon[10]$  as constants in hexadecimal before the key expansion Algorithm 2.2.

Starting from the 4 × 4 byte state, Fig. 2.3 shows the transformation it undergoes in a round (for  $1 \le r \le 9$ ).

#### 2.2.1.1 Software Implementations of AES

Of all operations, the **SubBytes** is the most difficult to implement. On 8-bit microcontrollers, a 256-byte look-up table is ideal to perform this operation. The table provides the necessary flexibility in terms of content, small footprint, and speed. For 32-bit platforms, more efficient implementations can be built using larger tables. We give a brief description of this method, which is known as *T*-table implementations. *T*-table implementations were first proposed in [5] and has been adopted by several crypto-libraries such as OpenSSL<sup>1</sup>.

Consider four look-up tables defined as follows:

$$\mathcal{T}_{0}[z] = \begin{bmatrix} 02 \bullet S(z) \\ S(z) \\ S(z) \\ 03 \bullet S(z) \end{bmatrix}; \mathcal{T}_{1}[z] = \begin{bmatrix} 03 \bullet S(z) \\ 02 \bullet S(z) \\ S(z) \\ S(z) \end{bmatrix}; \mathcal{T}_{2}[z] = \begin{bmatrix} S(z) \\ 03 \bullet S(z) \\ 02 \bullet S(z) \\ S(z) \end{bmatrix};$$

$$\mathcal{T}_{3}[z] = \begin{bmatrix} S(z) \\ S(z) \\ 03 \bullet S(z) \\ 03 \bullet S(z) \\ 02 \bullet S(z) \end{bmatrix};$$

(2.3)

Each table is of 1024 bytes mapping a byte z of the state to a 32-bit value. Using these tables, the first nine AES rounds can be expressed as follows

$$\begin{aligned} \mathbf{s}^{(r+1)} &= \mathcal{T}_0[s_0^{(r)}] \oplus \mathcal{T}_1[s_5^{(r)}] \oplus \mathcal{T}_2[s_{10}^{(r)}] \oplus \mathcal{T}_3[s_{15}^{(r)}] \oplus [k_0^{(r)} \ k_1^{(r)} \ k_2^{(r)} \ k_3^{(r)}]^T \| \\ & \mathcal{T}_0[s_4^{(r)}] \oplus \mathcal{T}_1[s_9^{(r)}] \oplus \mathcal{T}_2[s_{14}^{(r)}] \oplus \mathcal{T}_3[s_3^{(r)}] \oplus [k_4^{(r)} \ k_5^{(r)} \ k_6^{(r)} \ k_7^{(r)}]^T \| \\ & \mathcal{T}_0[s_8^{(r)}] \oplus \mathcal{T}_1[s_{13}^{(r)}] \oplus \mathcal{T}_2[s_2^{(r)}] \oplus \mathcal{T}_3[s_7^{(r)}] \oplus [k_8^{(r)} \ k_9^{(r)} \ k_{10}^{(r)} \ k_{11}^{(r)}]^T \| \\ & \mathcal{T}_0[s_{12}^{(r)}] \oplus \mathcal{T}_1[s_1^{(r)}] \oplus \mathcal{T}_2[s_6^{(r)}] \oplus \mathcal{T}_3[s_{11}^{(r)}] \oplus [k_{12}^{(r)} \ k_{13}^{(r)} \ k_{14}^{(r)} \ k_{15}^{(r)}]^T \end{aligned}$$

A byte of the state in the current round  $(\mathbf{s}^{(r)})$  is denoted  $s_i^{(r)}$  and the next round state is denoted  $\mathbf{s}^{(r+1)}$ , where  $0 \le r \le 9$  and  $0 \le i \le 15$ . The final round cannot use these tables due to the absence of the MixColumns operation.

<sup>&</sup>lt;sup>1</sup> http://www.openssl.org.

#### Fig. 2.3 Transformations of the state in a round of AES $(1 \le r \le 9)$

| $s_0$    | $s_4$ | $s_8$    | $s_{12}$ |  |

|----------|-------|----------|----------|--|

| $s_1$    | $s_5$ | $s_9$    | $s_{13}$ |  |

| $s_2$    | $s_6$ | $s_{10}$ | $s_{14}$ |  |

| $s_3$    | $s_7$ | $s_{11}$ | $s_{15}$ |  |

| <br>- 18 | 1     | 1        |          |  |

$s_i$  for  $0 \le i \le 15$  is the elements of the state

|          |          | SubByte     |             |  |

|----------|----------|-------------|-------------|--|

| $S(s_0)$ | $S(s_4)$ | $S(s_8)$    | $S(s_{12})$ |  |

| $S(s_1)$ | $S(s_5)$ | $S(s_9)$    | $S(s_{13})$ |  |

| $S(s_2)$ | $S(s_6)$ | $S(s_{10})$ | $S(s_{14})$ |  |

| $S(s_3)$ | $S(s_7)$ | $S(s_{11})$ | $S(s_{15})$ |  |

|          |          |             |             |  |

#### ShiftRows

| $S(s_0)$    | $S(s_4)$    | $S(s_8)$    | $S(s_{12})$ |

|-------------|-------------|-------------|-------------|

| $S(s_5)$    | $S(s_9)$    | $S(s_{13})$ | $S(s_1)$    |

| $S(s_{10})$ | $S(s_{14})$ | $S(s_2)$    | $S(s_6)$    |

| $S(s_{15})$ | $S(s_3)$    | $S(s_7)$    | $S(s_{11})$ |

|             |             |             |             |

#### MixColumns

|                                                                                    |                                                                                                          | V                                                                               |                                                                                                                        |

|------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| $2s_0'\oplus 3s_5'\oplus$                                                          | $2s'_4 \oplus 3s'_9 \oplus$                                                                              | $2s'_8 \oplus 3s'_{13} \oplus$                                                  | $2s_{12}^{\prime} \oplus 3s_{1}^{\prime} \oplus$                                                                       |

| $s'_{10} \oplus s'_{15}$                                                           | $s'_{14} \oplus s'_3$                                                                                    | $s'_2 \oplus s'_7$                                                              | $s_6' \oplus s_{11}'$                                                                                                  |

| $\begin{array}{c}s_0'\oplus 2s_5'\oplus\\3s_{10}'\oplus s_{15}'\end{array}$        | $\begin{array}{c}s_4'\oplus 2s_9'\oplus\\3s_{14}'\oplus s_3'\end{array}$                                 | $\begin{array}{c}s_8'\oplus 2s_{13}'\oplus\\ 3s_2'\oplus s_7'\end{array}$       | $\begin{array}{c}s_{12}^{\prime}\oplus 2s_{1}^{\prime}\oplus\\ 3s_{6}^{\prime}\oplus s_{11}^{\prime}\end{array}$       |

| $\begin{array}{c}s_0'\oplus s_5'\oplus\\2s_{10}'\oplus 3s_{15}'\end{array}$        | $\begin{array}{c}s_4^{\prime}\oplus s_9^{\prime}\oplus\\2s_{14}^{\prime}\oplus 3s_3^{\prime}\end{array}$ | $\begin{array}{c}s'_8 \oplus s'_{13} \oplus \\2s'_2 \oplus 3s'_7\end{array}$    | $\begin{array}{c}s_{12}^{\prime}\oplus s_{1}^{\prime}\oplus\\2s_{6}^{\prime}\oplus 3s_{11}^{\prime}\end{array}$        |

| $\begin{array}{c} 3s_0' \oplus s_5' \oplus \\ s_{10}' \oplus 2s_{15}' \end{array}$ | $\begin{array}{c} 3s'_4 \oplus s'_9 \oplus \\ s'_{14} \oplus 2s'_3 \end{array}$                          | $\begin{array}{c} 3s'_8 \oplus s'_{13} \oplus \\ s'_2 \oplus 2s'_7 \end{array}$ | $\begin{array}{c} 3s_{12}^{\prime} \oplus s_{1}^{\prime} \oplus \\ s_{6}^{\prime} \oplus 2s_{11}^{\prime} \end{array}$ |

| where                                                                              | $s_i' = S(s_i)$                                                                                          | for $0 \le i \le i$                                                             | $\leq 15$                                                                                                              |

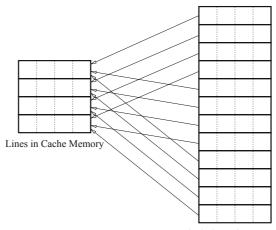

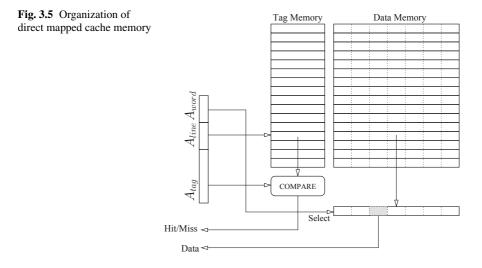

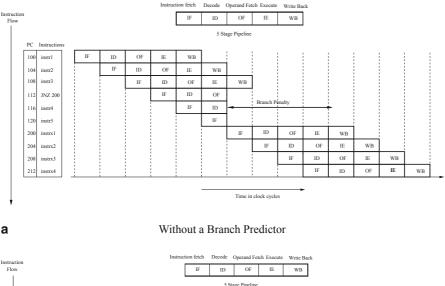

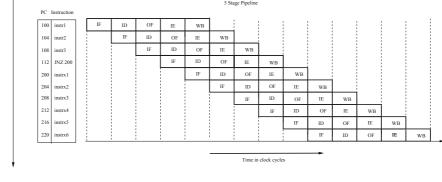

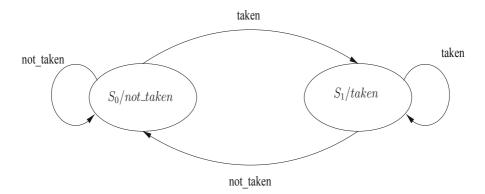

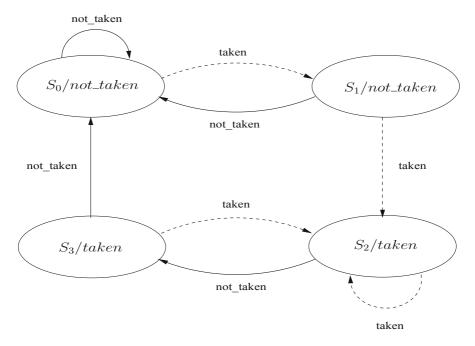

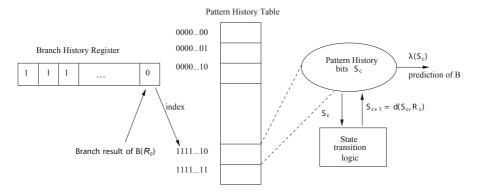

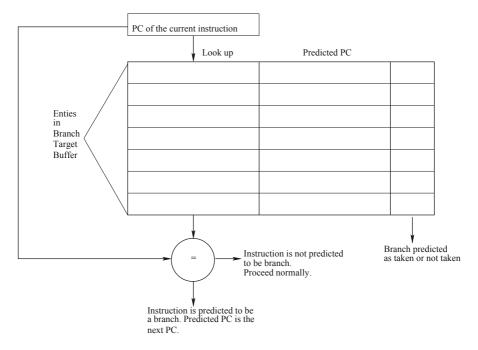

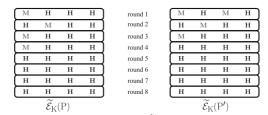

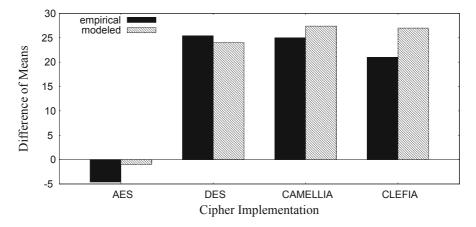

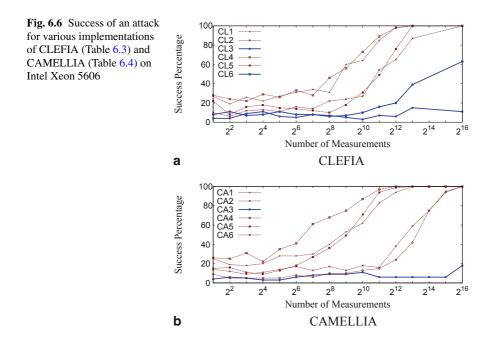

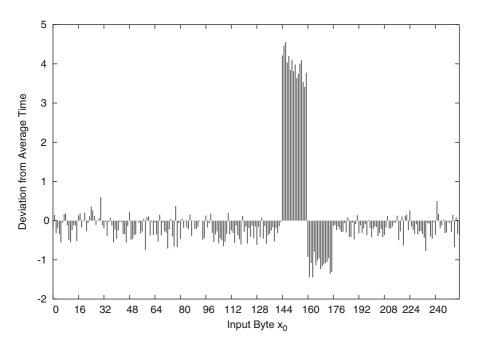

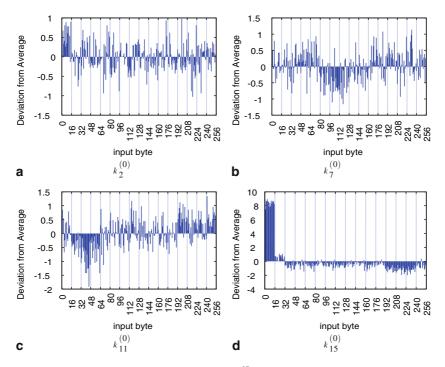

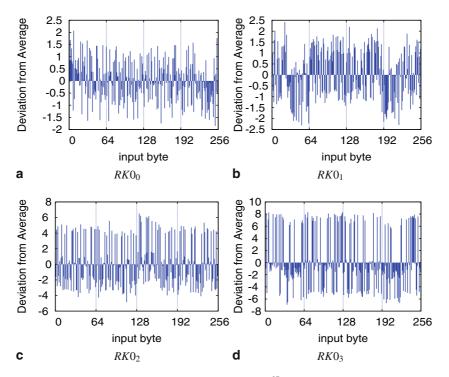

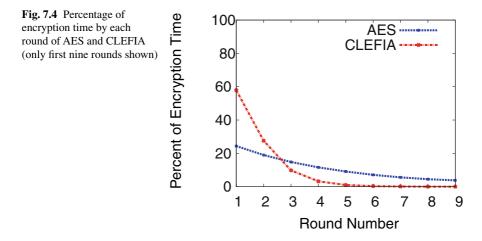

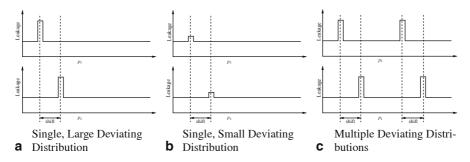

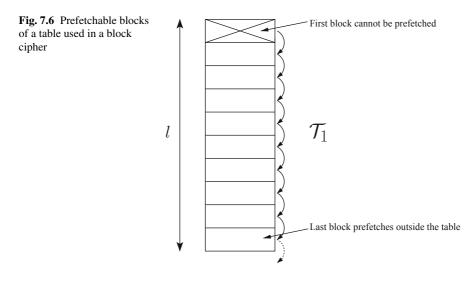

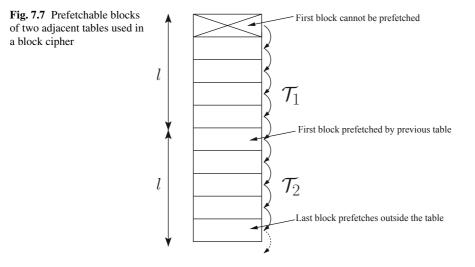

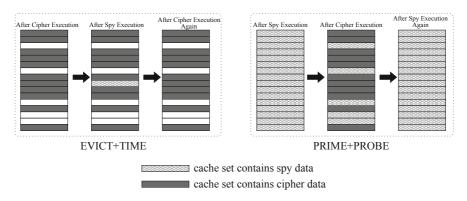

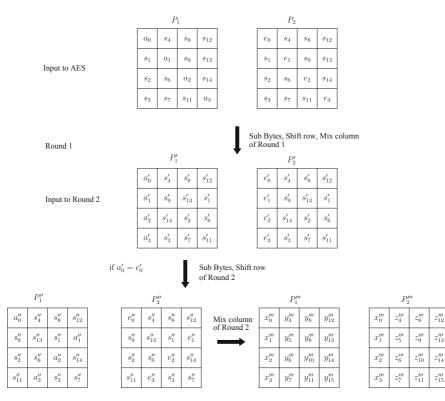

|                                                                                    |                                                                                                          | AddRou                                                                          | ndKey                                                                                                                  |